2次元で設計し、積層構造で実装していた従来のシステム・イン・パッケージ(SiP)では、今後主流となる3次元SiPの設計や、部品内蔵基板対応は困難です。また、SiP設計においては、システムとして回路情報を保ったまま設計することも必要です。さらに、実装設計においては、実装による電気特性、周辺の電磁界、熱、応力の影響など、さまざまな解析が必要ですが、それらを行うためのCADツール間にはデータの互換性がなく、統合的な解析が困難で、その結果実装設計のコストを押し上げていました。

STEERSIPは、そのような課題や要求に応える、フル3次元の半導体実装設計プラットフォームです。

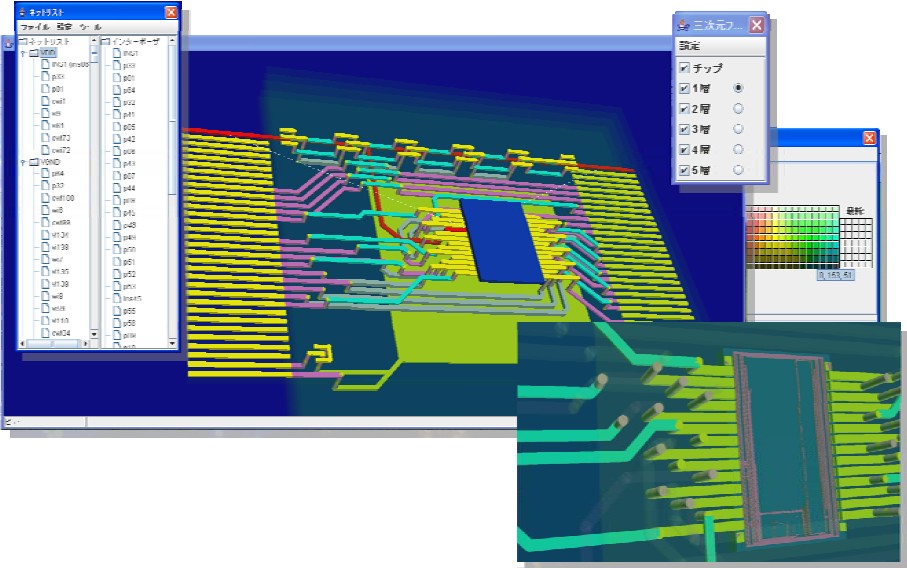

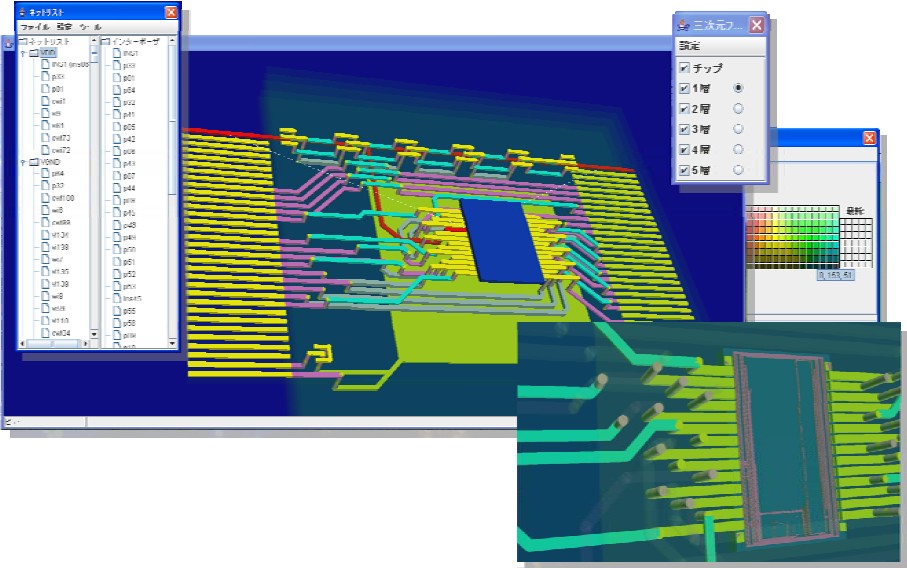

フル3次元編集対応

- すべての設計データは3次元データで保持し、表示・編集が可能。

豊富な自動編集機能

- SiP用の自動配置配線や自動計算機能(オプション)を用意しています。

各種解析ツールへのインタフェース

- 電磁界解析、熱解析、応力解析等のツールへのインタフェースを用意し、実装設計に必要な統合的な解析を可能にします。

業界標準データフォーマットのサポート

- STEERSIPは日本電子回路工業会標準 EB02、部品内蔵電子回路基板(部品内蔵基板) データフォーマットをサポートします

EB02フォーマットの入出力機能により、他のPCB設計ツール等とのインターオペラビリティー(相互運用性)を確保し、PCBデータを取り込んでSiPと一体化したシミュレーション等が可能になります。また他のシミュレーション、製造、テスト環境へのインタフェースが容易にできるようになります。

3次元チップ配置

-

- 3次元チップ配置

- フリップチップ、ワイヤボンディング対応

- 表裏面配置可能

3次元配線(ワイヤ、基板)

- ボンディングワイヤ入力(配線追従可能)

- 基板配線入力

SiP回路情報の入力

- SiP回路情報を入力し、自動配置配線で使用可能

- 3次元フライライン表示

チップデータの入力

- 半導体設計データを入力し、3次元表示、出力が可能

- MEMSの取り扱いが可能

配線チェッカー

- ボンディングワイヤの編集中チェック

- 基板配線の編集中チェック

チップデータの入力

3次元自動配置

2次元データビューワ

マスクデータ出力

JPCA標準EB02フォーマットの入出力

各種シミュレーション インタフェース

•

ケイレックスが提供するサービスのコア